## 16-bit Proprietary Microcontroller

**CMOS**

## F<sup>2</sup>MC-16L MB90660A Series

## MB90662A/663A/P663A

#### **■ DESCRIPTION**

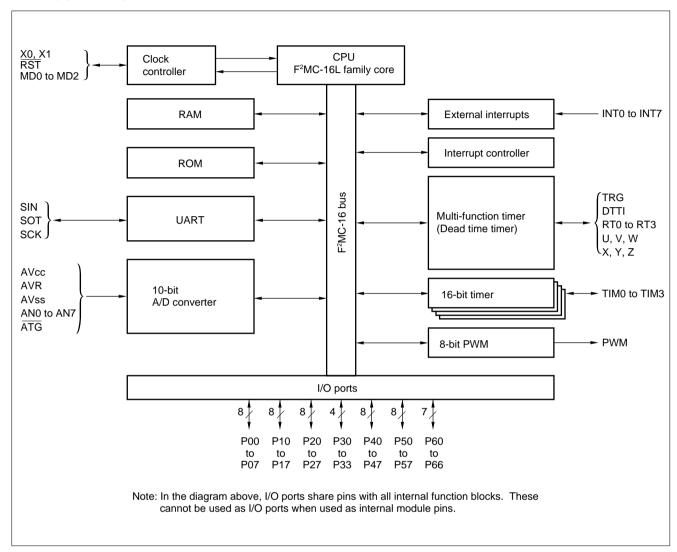

MB90660A series microcontrollers are 16-bit microcontrollers optimized for high speed realtime processing of consumer equipment and system control of air conditioner video cameras, VCRs, and copiers. Based on the F<sup>2</sup>MC\*-16 CPU core, an F<sup>2</sup>MC-16L is used as the CPU. This CPU includes high-level language-support instructions and robust task switching instructions, and additional addressing modes.

Microcontrollers in this series have built-in peripheral resources including multi-function timers, 16-bit reload timer four channels, 8-bit PWM one channel, UART one channel, 10-bit A/D eight converter channels, and external interrupt eight channels.

\*: F2MC stands for FUJITSU Flexible Microcontroller.

#### ■ FEATURES

- F<sup>2</sup>MC-16L CPU

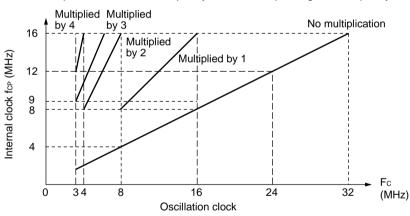

- Minimum execution time: 62.5 ns/4 MHz oscillation (uses PLL multiplier): fastest speed at quadruple operation

- Instruction set optimized for controller applications

Upward compatibility at object level with the F<sup>2</sup>MC-16(H)

Various data types (bit, byte, word, long-word)

Higher speed due to review of instruction cycle

Expanded addressing modes: 23 types

High coding efficiency

Two access methods (bank system or linear pointer)

Improved multiply-and-divide instructions (additional signed instructions)

Improved high-precision operation with 32-bit accumulator

Extended intelligent I/O services (access area extended by 64 Kbytes)

Large memory space: 16 Mbytes

(Continued)

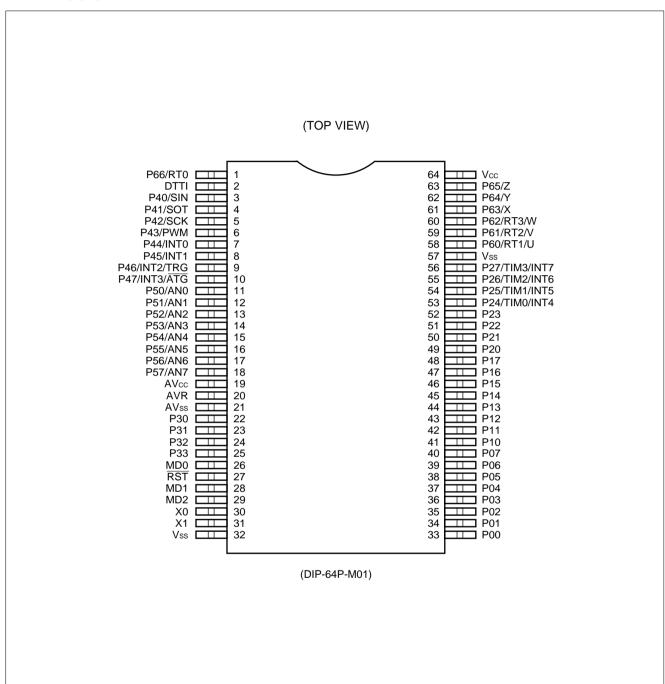

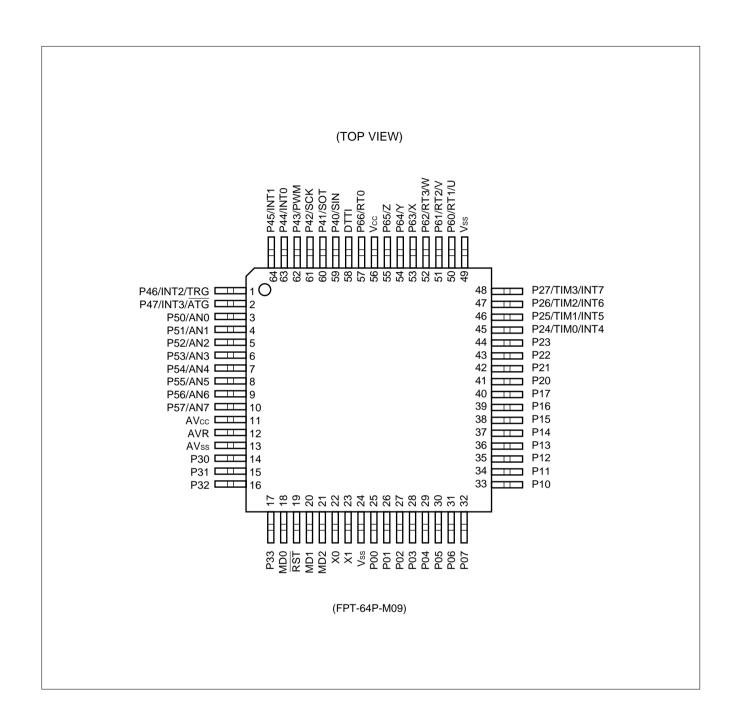

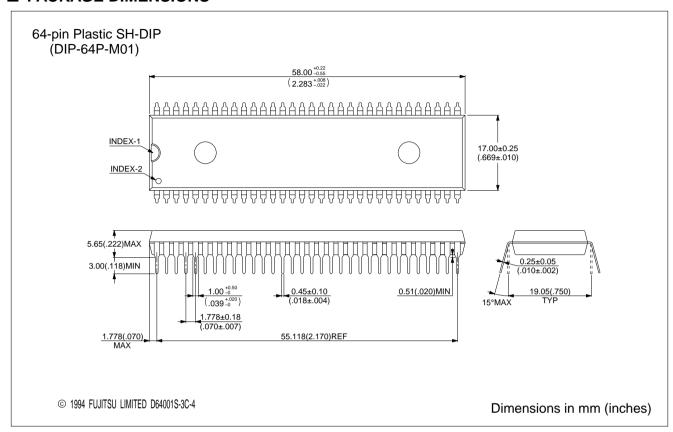

#### **■ PACKAGE**

64-pin Plastic SH-DIP

(DIP-64P-M01)

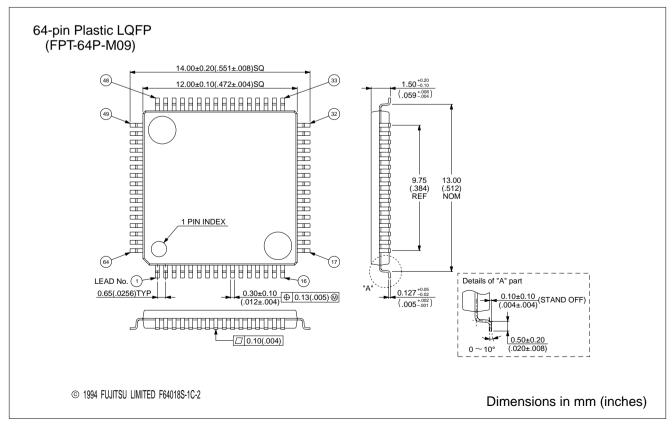

64-pin Plastic LQFP

(FPT-64P-M09)

#### (Continued)

• Improved instruction set applicable to high-level language (C) and multitasking

System stack pointer

Improved indirect instructions using various pointers

Barrel shift instruction

Stack check function

- Improved execution speed: 4-byte instruction queue

- Improved interrupt functions

- · Automatic data transfer function independent of CPU

#### Peripheral Resources

• ROM: 16 Kbytes (MB90661A)

32 Kbytes (MB90662A)

48 Kbytes (MB90663A)

One-time PROM: 48 Kbytes (MB90P663A)

• RAM: 512 bytes (MB90661A)

1.64 Kbytes (MB90662A)

2 Kbytes (MB90663A/MB90P663A)

• General-purpose ports: Max. 51

• UART: 1 channel

Can be used for both asynchronous transfer and clocked serial (I/O extended serial) communications

A/D converter: 10-bit, 8 channels Includes 8-bit conversion mode

• 16-bit reload timer: 4 channels

• 8-bit PWM: 1 channel

• External interrupts: 8 channels

- 18-bit timebase timer with watchdog timer function

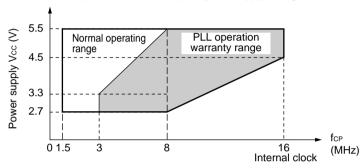

- PLL clock multiplier function

- CPU intermittent operation function

- · Various standby modes

- Package: SH-DIP-64/LQFP-64 (0.65-mm pitch)

- CMOS technology

# To Top / Lineup / Index MB90660A Series

#### **■ PRODUCT LINEUP**

| Part number Parameter   | MB90P663A                                                                                                                               | MB90662A                                                                                                                                                                                                                                           | MB90663A                    |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|

| Classification          | OTPROM                                                                                                                                  | MASK ROM                                                                                                                                                                                                                                           | MASK ROM                    |  |  |  |  |

| ROM size                | 48 Kbytes                                                                                                                               | 32 Kbytes                                                                                                                                                                                                                                          | 48 Kbytes                   |  |  |  |  |

| RAM size                | 2 Kbytes                                                                                                                                | 1.64 Kbytes                                                                                                                                                                                                                                        | 2 Kbytes                    |  |  |  |  |

| CPU functions           | Number of basic instructions Instruction bit length Instruction length Data bit length Minimum execution time Interrupt processing time | : 340<br>: 8/16 bits<br>: 1 to 7 bytes<br>: 1, 4, 8, 16, or 32 bits<br>: 62.5 ns/4 MHz (PLL 4 mul<br>: 1000 ns/16 MHz (minimun                                                                                                                     |                             |  |  |  |  |

| Ports                   | Input Ports I/O ports (CMOS) I/O ports (N channel open-dra Total                                                                        | /O ports (CMOS) : 39<br>/O ports (N channel open-drain) : 8                                                                                                                                                                                        |                             |  |  |  |  |

| Packages                | DIP-64P-M01<br>FPT-64P-M09                                                                                                              | DIP-64P-M01<br>FPT-64P-M09                                                                                                                                                                                                                         | DIP-64P-M01<br>FPT-64P-M09  |  |  |  |  |

| Multi-Function<br>Timer | register, zero detect terminal c                                                                                                        | , buffered compare register × 4 control, 4 output channels, non-dead time timer, 4-bit carrier co                                                                                                                                                  | overlapped 3-phase waveform |  |  |  |  |

| UART                    | Full duplex double buffer<br>Selectable clock synchronous,<br>Built-in dedicated baud rate go<br>19230, 9615, 4808, 2404, 120           | Selectable clock synchronous/asynchronous operation Built-in dedicated baud rate generator (During asynchronous operation: 62500, 31250,                                                                                                           |                             |  |  |  |  |

| A/D Converter           | 10-bit precision × 8 channels A/D conversion time  Startup trigger  Activiation                                                         | 10-bit precision × 8 channels A/D conversion time  : 6.13 μs (98 machine cycles at 16 MHz machine clock, includes sample hold time)  Startup trigger  : Startup by software, external source, or multi-function timer output (RT0) can be selected |                             |  |  |  |  |

| 16-Bit Reload<br>Timer  |                                                                                                                                         | toggle output, one-shot output s<br>from 0.125 μs, 0.5 μs, or 2.0 μs<br>e                                                                                                                                                                          |                             |  |  |  |  |

| 8-Bit PWM               |                                                                                                                                         | n (arbitrary cycle: duty ratio pul<br>from 0.125 μs or 64.0 μs at 16                                                                                                                                                                               |                             |  |  |  |  |

| External Interrupts     | Number of inputs: 8<br>External interrupt mode (Intersources)                                                                           | External interrupt mode (Interrupts can be generated by four types of request detect                                                                                                                                                               |                             |  |  |  |  |

| PLL Function            | 1/2/3/4-time multiplier can be operation frequency)                                                                                     | 1/2/3/4-time multiplier can be selected (Please set so as not to exceed guaranteed operation frequency)                                                                                                                                            |                             |  |  |  |  |

| Miscellaneous<br>Items  | V <sub>PP</sub> is shared with MD2<br>terminal (when writing the<br>EPROM)                                                              | _                                                                                                                                                                                                                                                  | _                           |  |  |  |  |

#### **■ PIN ASSIGNMENT**

#### **■ PIN DESCRIPTION**

| Pin      | no.      |              | Circuit       |                                                                                                                                                                                                                                                                                                                                                  |  |

|----------|----------|--------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SH-DIP*1 | LQFP*2   | Pin name     | type          | Function                                                                                                                                                                                                                                                                                                                                         |  |

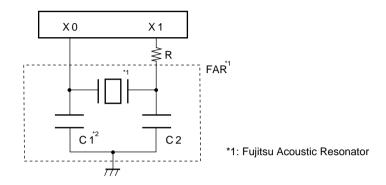

| 30       | 22       | X0           | А             | Crystal oscillator pin (32 MHz).                                                                                                                                                                                                                                                                                                                 |  |

| 31       | 23       | X1           | (Oscillator)  |                                                                                                                                                                                                                                                                                                                                                  |  |

| 33 to 40 | 25 to 32 | P00 to P07   | B<br>(CMOS)   | General-purpose I/O ports.                                                                                                                                                                                                                                                                                                                       |  |

| 41 to 48 | 33 to 40 | P10 to P17   | B<br>(CMOS)   | General-purpose I/O ports.                                                                                                                                                                                                                                                                                                                       |  |

| 49 to 52 | 41 to 44 | P20 to P23   | B<br>(CMOS)   | General-purpose I/O ports.                                                                                                                                                                                                                                                                                                                       |  |

| 53 to 56 | 45 to 48 | P24 to P27   | G<br>(CMOS)   | General-purpose I/O ports. This function is activated when the output specification of the reload timer is "disabled".                                                                                                                                                                                                                           |  |

|          |          | TIM0 to TIM3 |               | I/O pins for reload timers 0 to 4. Input is used only as necessary while serving as input for the reload timer. It is therefore necessary to stop output beforehand using other functions unless intentionally used otherwise.  Their function as output terminals for the reload timer is activated when the output specification is "enabled". |  |

|          |          | INT4 to INT7 |               | External interrupt request input pins. Input is used only as necessary while external interrupts are enabled. It is therefore necessary to stop output beforehand using other functions unless intentionally used otherwise.                                                                                                                     |  |

| 22 to 25 | 14 to 17 | P30 to P33   | B<br>(CMOS)   | General-purpose I/O ports.                                                                                                                                                                                                                                                                                                                       |  |

| 3        | 59       | P40          | E<br>(CMOS/H) | General-purpose I/O port. This function is always enabled.                                                                                                                                                                                                                                                                                       |  |

|          | SIN      |              |               | UART serial data input pin. Input is used only as necessary while serving as UART input. It is therefore necessary to stop output beforehand using other functions unless intentionally used otherwise.                                                                                                                                          |  |

| 4        | 60       | P41          | E<br>(CMOS/H) | General-purpose I/O port. This function is activated when the serial data output specification of the UART is "disabled".                                                                                                                                                                                                                        |  |

| S        |          | SOT          |               | UART serial data output pin. This function is activated when the serial data output specification of the UART is "enabled".                                                                                                                                                                                                                      |  |

\*1: DIP-64P-M01

\*2: FPT-64P-M09

# To Top / Lineup / Index MB90660A Series

| Pin          | no.     | Dia          | Circuit       | Function                                                                                                                                                                                                                                                                                 |  |  |  |

|--------------|---------|--------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SH-DIP*1     | LQFP*2  | Pin name     | type          |                                                                                                                                                                                                                                                                                          |  |  |  |

| 5            | 61      | P42          | E<br>(CMOS/H) | General-purpose I/O port. This function is activated when the clock output specification of the UART is "disabled".                                                                                                                                                                      |  |  |  |

|              |         | SCK          |               | UART clock I/O pin. This function is activated when the clock output specification of the UART is "enabled". Input is used only as necessary while serving as UART input. It is therefore necessary to stop output beforehand using other functions unless intentionally used otherwise. |  |  |  |

| 6            | 62      | P43          | E<br>(CMOS/H) | General-purpose I/O port. This function is activated when the output specification of the PWM is "disabled".                                                                                                                                                                             |  |  |  |

|              |         | PWM          |               | PWM timer output pin. This function is activated when the waveform output specification of the PWM timer is "enabled".                                                                                                                                                                   |  |  |  |

| 7 63<br>8 64 |         | P44 to P45   | D<br>(CMOS/H) | General-purpose I/O ports. This function is always active.                                                                                                                                                                                                                               |  |  |  |

|              |         | INT0 to INT1 |               | External interrupt request input pins. Input is used only as necessary while external interrupts are enabled.                                                                                                                                                                            |  |  |  |

| 9            | 1       | P46          | D<br>(CMOS/H) | General-purpose input port. This function is always active.                                                                                                                                                                                                                              |  |  |  |

|              |         | INT2         |               | External interrupt request input pin. Input is used only as necessary while external interrupts are enabled.                                                                                                                                                                             |  |  |  |

|              |         | TRG          |               | Timer clear trigger input pin for multi-function timer. Input is used only as necessary while multi-function timer input is enabled.                                                                                                                                                     |  |  |  |

| 10           | 2       | P47          | D<br>(CMOS/H) | General-purpose input port. This function is always active.                                                                                                                                                                                                                              |  |  |  |

|              |         | INT3         |               | External interrupt request input pin. Input is used only as necessary while external interrupts are enabled.                                                                                                                                                                             |  |  |  |

|              |         | ĀTG          |               | Trigger input pin for the A/D converter. Input is used only as necessary while the A/D converter is performing input.                                                                                                                                                                    |  |  |  |

| 11 to 18     | 3 to 10 | P50 to P57   | C<br>(AD)     | Open-drain type I/O ports. This function is enabled when the analog input enable register specification is "port".                                                                                                                                                                       |  |  |  |

|              |         | AN0 to AN7   |               | Analog input pins for the A/D converter. This function is enabled when the analog input enable register specification is "AD".                                                                                                                                                           |  |  |  |

\*1: DIP-64P-M01

\*2: FPT-64P-M09

| Pin             | no. | D:       | Circuit       | Function                                                                                                                                                                                  |  |  |  |

|-----------------|-----|----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SH-DIP*1 LQFP*2 |     | Pin name | type          | Function                                                                                                                                                                                  |  |  |  |

| 58 50           |     | P60      | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the multi-function timer waveform output specification is "disabled" and the 3-phase waveform output specification is "disabled". |  |  |  |

|                 |     | RT1      |               | Multi-function timer waveform output pin. This function is enabled when the multi-function timer output specification is "enabled".                                                       |  |  |  |

|                 |     | U        |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                                                                        |  |  |  |

| 59              | 51  | P61      | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the multi-function timer waveform output specification is "disabled" and the 3-phase waveform output specification is "disabled". |  |  |  |

|                 |     | RT2      |               | Multi-function timer waveform output pin. This function is enabled when the multi-function timer output specification is "enabled".                                                       |  |  |  |

|                 |     | V        |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                                                                        |  |  |  |

| 60              | 52  | P62      | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the multi-function timer waveform output specification is "disabled" and the 3-phase waveform output specification is "disabled". |  |  |  |

|                 |     | RT3      |               | Multi-function timer waveform output pin. This function is enabled when the multi-function timer output specification is "enabled".                                                       |  |  |  |

|                 |     | W        |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                                                                        |  |  |  |

| 61              | 53  | P63      | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the 3-phase waveform output specification is "disabled".                                                                          |  |  |  |

|                 |     | X        |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                                                                        |  |  |  |

| 62 54           |     | P64      | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the 3-phase waveform output specification is "disabled".                                                                          |  |  |  |

|                 |     | Υ        |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                                                                        |  |  |  |

\*1: DIP-64P-M01

\*2: FPT-64P-M09

# To Top / Lineup / Index MB90660A Series

#### (Continued)

| Pin            | no.            | Pin name   | Circuit       | Funation                                                                                                                            |

|----------------|----------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| SH-DIP*1       | LQFP*2         | - Pin name | type          | Function                                                                                                                            |

| 63 55          |                | P65        | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the 3-phase waveform output specification is "disabled".                    |

|                |                | Z          |               | 3-phase waveform output pin. This function is enabled when the 3-phase waveform output specification is "enabled".                  |

| 1              | 57             | P66        | E<br>(CMOS/H) | General-purpose I/O port. This function is enabled when the multi-function timer waveform output specification is "disabled".       |

|                |                | RT0        |               | Multi-function timer waveform output pin. This function is enabled when the multi-function timer output specification is "enabled". |

| 2              | 58             | DTTI       | D<br>(CMOS/H) | 3-phase waveform output disable input (DTTI) pin.                                                                                   |

| 19             | 11             | AVcc       | Power supply  | Power supply for analog circuits. Turn this power supply on/off by applying a voltage level greater than AVcc to Vcc.               |

| 20             | 12             | AVR        | Power supply  | Reference power supply for analog circuits. Turn this pin on/off by applying a voltage level greater than AVR to AVcc.              |

| 21             | 13             | AVss       | Power supply  | Ground level for analog circuits.                                                                                                   |

| 26<br>28<br>29 | 18<br>20<br>21 | MD0 to MD2 | F<br>(CMOS/H) | Input pins for specifying operation mode. Use these pins by directly connecting to Vcc or Vss.                                      |

| 27             | 19             | RST        | D<br>(CMOS/H) | External reset request input pin.                                                                                                   |

| 64             | 56             | Vcc        | Power supply  | Power supply for digital circuits.                                                                                                  |

| 32<br>57       | 24<br>49       | Vss        | Power supply  | Ground level for digital circuits.                                                                                                  |

\*1: DIP-64P-M01 \*2: FPT-64P-M09

#### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                | Remarks                                                                                                                |

|------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

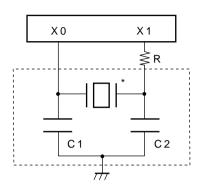

| A    | X1  X0  Clock input  Standby control signal                            | <ul> <li>3 MHz to 32 MHz operation</li> <li>Oscillation feedback resistor: Approx. 1 MΩ</li> </ul>                     |

| В    | Digital output  Digital output  Digital input  Standby control  Signal | CMOS level input and output     With standby control     Pull-up option can be selected     With standby control       |

| С    | Digital output  A/D input  Digital input  A/D disable                  | N-channel open-drain output<br>CMOS level hysteresis input<br>With A/D control                                         |

| D    | Digital input                                                          | CMOS level hysteresis input     Without standby control     Pull-up option can be selected     Without standby control |

# To Top / Lineup / Index MB90660A Series

| Туре | Circuit                                                       | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Е    | Digital output  Digital output  Digital output  Digital input | CMOS level output CMOS level hysteresis input With standby control Pull-up option can be selected With standby control                                                                                                                                                                                                                                                                                                            |

| F    | Noise filter Digital input Typ. 40 ns                         | <ul> <li>CMOS level input         (Mask ROM version uses CMOS hysteresis input)         Without standby control</li> <li>Pull-up option can be selected for MD2 (*1)         Pull-up option can be selected for MD1/0 (*2)         Both without standby option</li> <li>The MB90P663A does not include a noise filter.         It also does not have a P channel protect Tr (*3)         for the MD2 pin or pull-down.</li> </ul> |

| G    | Digital output  Digital output  Digital input                 | CMOS level input and output     Without standby control     Pull-up option can be selected     With standby control                                                                                                                                                                                                                                                                                                               |

#### **■ HANDLING DEVICES**

#### 1. Preventing Latchup

Latchup may occur with CMOS ICs if voltage higher than Vcc or lower than Vss is applied to input and output pins other than medium- to high-voltage pins or if higher than the voltage which shows on "1. Absolute Maximum Ratings" in section "■ Electrical Characteristics" is applied between Vcc and Vss.

When latchup occurs, power supply current increases rapidly and might thermally damage elements. When using, take great care not to exceed the absolute maximum ratings.

To prevent the similar aftereffects, use also the utmost care not to allow the analog supply voltage to exceed the digital supply voltage.

#### 2. Treatment of Unused Input Pins

Leaving unused input pins open could cause malfunctions. They should be pins should be connected to a pull-up or pull-down resistor.

#### 3. External Reset Input

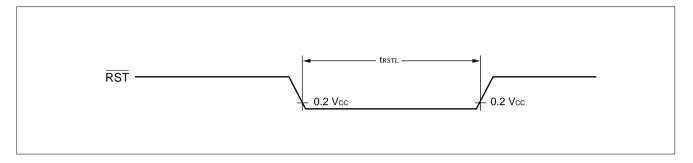

When resetting by inputting "L" level to the  $\overline{RST}$  pin, the "L" level must be input for at least 5 machine cycles to ensure that internal reset has occurred. Be aware of this point when using external clock input.

#### 4. Vcc, Vss Pin

Be sure that both Vcc and Vss are at the same voltage.

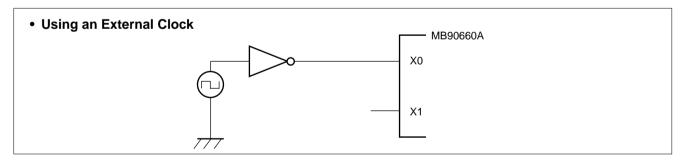

#### 5. Notes on Using an External Clock

Drive X0 when using an external clock.

#### 6. Order of Power-on to A/D Converter and Analog Inputs

Power-off (AVcc, AVR) to the digital power supply (Vcc) must be performed only after the A/D converter and the analog inputs (AN0 to AN7) has been turned on.

Turning on or off should always be performed keeping AVR below AVcc.

Use caution for the input voltage not to exceed AVcc when the pin sharing the analog input for its function is used as an input port.

#### 7. Programming Mode

When the MB90P663A is shipped from Fujitsu, all bits ( $48 \text{ K} \times 8 \text{ bits}$ ) are set to "1". Program by setting selected bits to "0" when you wish to set the data. Note that "1" cannot be programming electrically.

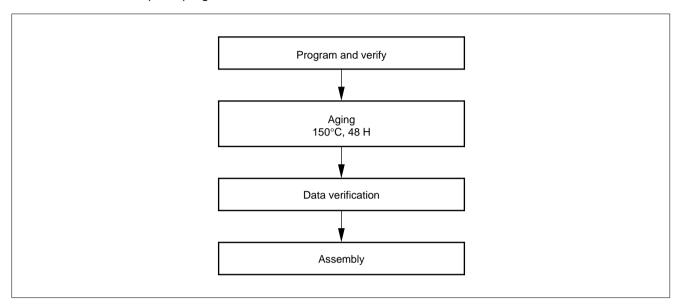

#### 8. Recommended Screening Conditions

High-temperature aging is recommended as the pre-assembly screening procedure for a product with a blanked OTPROM microcomputer program.

#### 9. Programming Yields

All bits cannot be programmed at Fujitsu shipping test to a blanked OTPROM microcomputer, due to its nature. For this reason, a programming yield of 100% cannot be assured at all times.

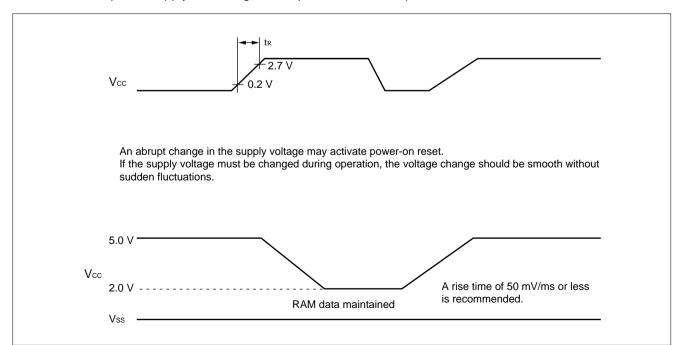

#### 10.Fluctuations in Supply Voltage

Although the assured  $V_{\rm CC}$  supply voltage operating range is as specified, sudden fluctuations even within this range may cause a malfunction. Therefore, the voltage supply to the IC should be kept as constant as possible. The  $V_{\rm CC}$  ripple (P-P value) at the supply frequency (50 to 60 Hz) should be less than 10% of the typical  $V_{\rm CC}$  value, or the coefficient of excessive variation should not be more than 0.1 V/ms instantaneous change when power is supplied.

#### ■ PROGRAMMING THE MB90P663A EPROM

Since the MB90P663A is functionally equivalent to the MBM27C1000 when it is in EPROM mode, it is possible to program them with a general-purpose EPROM programmer by using a special adaptor socket.

However, the MB90660A does not support the electronic signature (device ID code) mode.

#### 1. Pin Assignment in EPROM Mode

#### • MBM27C1000-compatible pins

| MBM2    | 7C1000          | MB90P663A |      |                        | MBM2    | MBM27C1000 |         |      | MB90P663A |  |  |

|---------|-----------------|-----------|------|------------------------|---------|------------|---------|------|-----------|--|--|

| Din no  | Din nama        | Pin       | no.  | Din nomo               | Pin no. | Pin name   | Pin no. |      | D'        |  |  |

| Pin no. | Pin name        | SH-DIP    | LQFP | Pin name               | Pin no. | Pin name   | SH-DIP  | LQFP | Pin name  |  |  |

| 1       | V <sub>PP</sub> | 29        | 21   | MD2 (V <sub>PP</sub> ) | 32      | Vcc        | 64      | 56   | Vcc       |  |  |

| 2       | ŌĒ              | 24        | 16   | P32                    | 31      | PGM        | 25      | 17   | P33       |  |  |

| 3       | A15             | 48        | 40   | P17                    | 30      | NC         | _       |      | _         |  |  |

| 4       | A12             | 45        | 37   | P14                    | 29      | A14        | 47      | 39   | P16       |  |  |

| 5       | A07             | 56        | 48   | P27                    | 28      | A13        | 46      | 38   | P15       |  |  |

| 6       | A06             | 55        | 47   | P26                    | 27      | A08        | 41      | 33   | P10       |  |  |

| 7       | A05             | 54        | 46   | P25                    | 26      | A09        | 42      | 34   | P11       |  |  |

| 8       | A04             | 53        | 45   | P24                    | 25      | A11        | 44      | 36   | P13       |  |  |

| 9       | A03             | 52        | 44   | P23                    | 24      | A16        | 22      | 14   | P30       |  |  |

| 10      | A02             | 51        | 43   | P22                    | 23      | A10        | 43      | 35   | P12       |  |  |

| 11      | A01             | 50        | 42   | P21                    | 22      | CE         | 23      | 15   | P31       |  |  |

| 12      | A00             | 49        | 41   | P20                    | 21      | D07        | 40      | 32   | P07       |  |  |

| 13      | D00             | 33        | 25   | P00                    | 20      | D06        | 39      | 31   | P06       |  |  |

| 14      | D01             | 34        | 26   | P01                    | 19      | D05        | 38      | 30   | P05       |  |  |

| 15      | D02             | 35        | 27   | P02                    | 18      | D04        | 37      | 29   | P04       |  |  |

| 16      | GND             | _         | _    | _                      | 17      | D03        | 36      | 28   | P03       |  |  |

#### • Power supply, GND connection pins

| Type  | Pin    | no.  | Pin name |

|-------|--------|------|----------|

| Туре  | SH-DIP | LQFP | Pin name |

| Power | 2      | 58   | DTTI     |

|       | 64     | 56   | Vcc      |

| GND   | 57     | 49   | Vss      |

|       | 21     | 13   | AVss     |

|       | 27     | 19   | RST      |

|       | 32     | 24   | Vss      |

|       | 26     | 18   | MD0      |

|       | 3      | 59   | P40      |

|       | 4      | 60   | P41      |

|       | 5      | 61   | P42      |

#### • Pins other than MBM27C1000-compatible pins

| Pin                                                        | no.                                    | Pin name                                                                   | Processing                                        |  |  |

|------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------|--|--|

| SH-DIP                                                     | LQFP                                   | Fili Haille                                                                | Frocessing                                        |  |  |

| 30<br>28                                                   | 22<br>20                               | X0<br>MD1                                                                  | Pull-up by<br>4.7 KΩ                              |  |  |

| 31                                                         | 23                                     | X1                                                                         | OPEN                                              |  |  |

| 9<br>10<br>11 to 18<br>19<br>20<br>58 to 63<br>1<br>6 to 8 | 1 2 3 to 10 11 12 50 to 55 57 62 to 64 | P46<br>P47<br>P50 to P57<br>AVcc<br>AVR<br>P60 to P65<br>P66<br>P43 to P45 | 1 MΩ-level pull-up resistor connected to each pin |  |  |

#### 2. EPROM Programmer Socket Adapter and Recommended Programmer Manufacturer

| Part no.    | Package   | Compatible socket adapter | Recommended programmer manufacturer and programmer name |                    |                 |  |  |

|-------------|-----------|---------------------------|---------------------------------------------------------|--------------------|-----------------|--|--|

|             | rackage   | Sun Hayato Co., Ltd.      | Minato<br>Electronics Inc.                              | Data I/O Co., Ltd. | Advantest Corp. |  |  |

| MB90P663AP  | SH-DIP-64 | ROM-64SD-32DP-16L         | Recommended                                             | Recommended        | Recommended     |  |  |

| MB90P663APF | LQFP-64   | ROM-64SF-32DP-16L         | Recommended                                             | Recommended        | Recommended     |  |  |

Inquiry: Sun Hayato Co., Ltd.: TEL (81)-3-3986-0403 FAX (81)-3-5396-9106

Minato Electronics Inc.: TEL: USA (1)-916-348-6066

JAPAN (81)-45-591-5611

Data I/O Co., Ltd.: TEL: USA/ASIA (1)-206-881-6444

EUROPE (49)-8-985-8580

Advantest Corp.: TEL: Except JAPAN (81)-3-3930-4111

#### 3. Programming Data

- (1) Adjust the EPROM programmer to settings for the MBM27C1000.

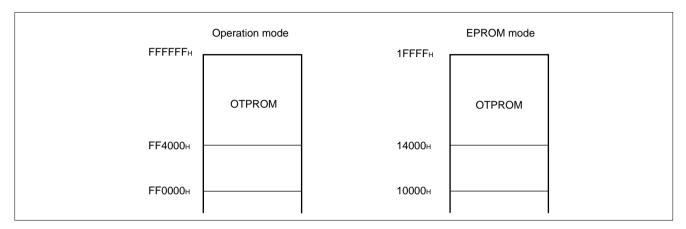

- (2) Load program data from addresses 10000<sub>H</sub> to 1FFFF<sub>H</sub> in the EPROM programmer.

OTPROM addresses FF4000<sub>H</sub> to FFFFFF<sub>H</sub> of the MB90P663A in operation mode correspond to addresses 14000<sub>H</sub> to 1FFFF<sub>H</sub> in EPROM mode.

- (3) Set the MB90P663A into the adaptor socket and install the adaptor socket into the EPROM programmer. Pay attention to the orientation of the device and the adaptor socket at this time.

- (4) Programming data to the EPROM.

- (5) If data cannot be programmed, try again with a 0.1 μF capacitor connected between Vcc and GND and VPP and GND.

Note: Since Mask ROM products (MB90662A/663A) do not include an EPROM mode, data cannot be read-out using an EPROM programmer.

#### 4. PROM Option Bitmap

The programming method is the same as a PROM, and can be set by programming values to addresses indicated in the memory map.

The following bit map shows the relation between bits and options.

#### PROM Option Bitmap

| Address Bit  | 7                                 | 6                                 | 5                                 | 4                                 | 3                                 | 2                                  | 1                                      | 0                                       |

|--------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|------------------------------------|----------------------------------------|-----------------------------------------|

| 00004н       | P07                               | P06                               | P05                               | P04                               | P03                               | P02                                | P01                                    | P00                                     |

|              | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                            | Pull-up                                | Pull-up                                 |

|              | 1: No                              | 1: No                                  | 1: No                                   |

|              | 0: Yes                             | 0: Yes                                 | 0: Yes                                  |

| 00008н       | P17                               | P16                               | P15                               | P14                               | P13                               | P12                                | P11                                    | P10                                     |

|              | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                            | Pull-up                                | Pull-up                                 |

|              | 1: No                              | 1: No                                  | 1: No                                   |

|              | 0: Yes                             | 0: Yes                                 | 0: Yes                                  |

| 0000Сн       | P27                               | P26                               | P25                               | P24                               | P23                               | P22                                | P21                                    | P20                                     |

|              | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                            | Pull-up                                | Pull-up                                 |

|              | 1: No                              | 1: No                                  | 1: No                                   |

|              | 0: Yes                             | 0: Yes                                 | 0: Yes                                  |

| 00010н       | P43                               | P42                               | P41                               | P40                               | P33                               | P32                                | P31                                    | P30                                     |

|              | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                           | Pull-up                            | Pull-up                                | Pull-up                                 |

|              | 1: No                              | 1: No                                  | 1: No                                   |

|              | 0: Yes                             | 0: Yes                                 | 0: Yes                                  |

| 00014н<br>*1 | P47<br>Pull-up<br>1: No<br>0: Yes | P46<br>Pull-up<br>1: No<br>0: Yes | P45<br>Pull-up<br>1: No<br>0: Yes | P44<br>Pull-up<br>1: No<br>0: Yes | RST<br>Pull-up<br>1: No<br>0: Yes | DTTI<br>Pull-up<br>1: No<br>0: Yes | Accept asynchronous reset 1: Yes 0: No | MD1/MD0°2<br>Pull-up<br>1: No<br>0: Yes |

| 00018н       | Open                              | P66<br>Pull-up<br>1: No<br>0: Yes | P65<br>Pull-up<br>1: No<br>0: Yes | P64<br>Pull-up<br>1: No<br>0: Yes | P63<br>Pull-up<br>1: No<br>0: Yes | P62<br>Pull-up<br>1: No<br>0: Yes  | P61<br>Pull-up<br>1: No<br>0: Yes      | P60<br>Pull-up<br>1: No<br>0: Yes       |

Initially (value when blank), all bits are "1".

- \*1: Under this release, the pull-up resistor is cut-off during stop mode for pins for which the pull-up option was selected. (Pins for which the circuit type shown in the "■ Pin Description" is B or E.)

However, the pull-up resistor is not cut-off even in stop mode for P44 to 47, RST, DTTI (pins for which the circuit type shown in the "■ Pin Description" is D or G), and MD1 and MD0.

- \*2: Whether or not a pull-up/pull-down resistor is present for MD2, MD1 and MD0 is determined as follows. If pull-up/pull-down resistor is selected, it is included with all 2 (or 3) pins. Presence or absence of the pull-up or pull-down resistors for the mode terminal cannot be selected for each pin.

| Pin | MB90P663A             | MB90663A/2A               |

|-----|-----------------------|---------------------------|

| MD2 | No                    | Pull-down can be selected |

| MD1 | With pull-up resistor | With pull-up resistor     |

| MD0 | With pull-up resistor | With pull-up resistor     |

Notes: • "FFH" must be set to addresses no defined in the table above.

Since the option setting for the MB90P663A takes 8 machine cycles, the option setting is not made until

a clock is provided after power-on. (This results in no pull-up for all pins, and asynchronous reset input is

accepted.)

#### **■ BLOCK DIAGRAM**

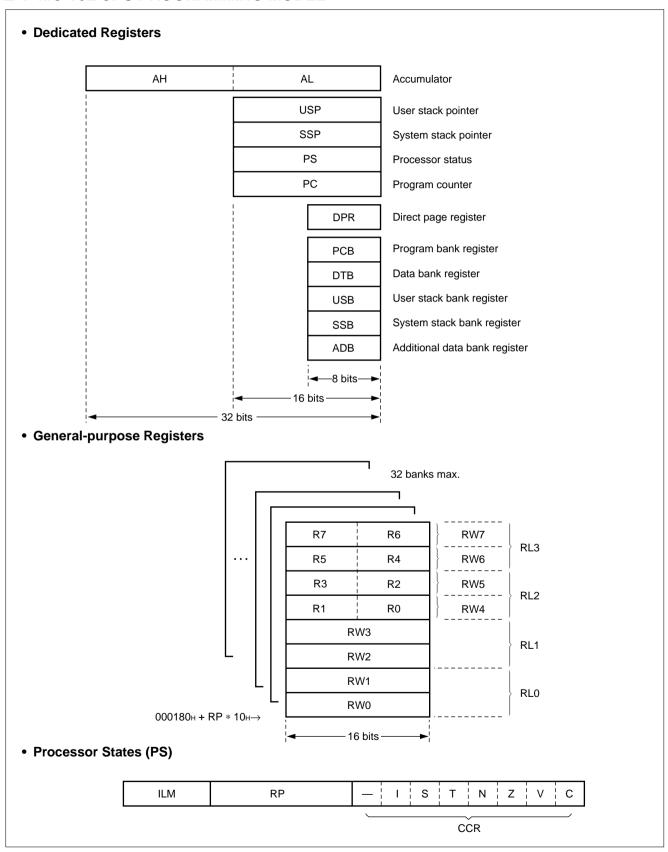

#### ■ F<sup>2</sup>MC-16L CPU PROGRAMMING MODEL

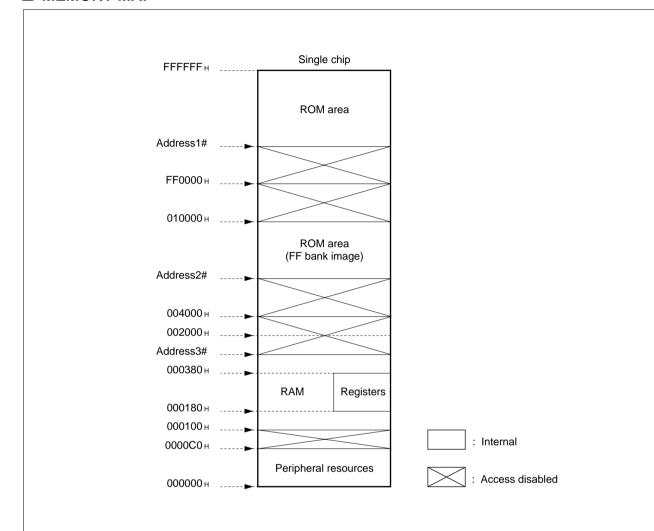

#### **■ MEMORY MAP**

| Product Model | Address #1          | Address #2 | Address #3 |

|---------------|---------------------|------------|------------|

| MB90662A      | FF8000 <sub>H</sub> | 008000н    | 000780н    |

| MB90663A      | FF4000 <sub>H</sub> | 004000н    | 000900н    |

| MB90P663A     | FF4000 <sub>H</sub> | 004000н    | 000900н    |

# To Top / Lineup / Index MB90660A Series

#### ■ I/O MAP

| Address           | Register                                                   | Name          | Access*2 | Resource name      | Initial value |

|-------------------|------------------------------------------------------------|---------------|----------|--------------------|---------------|

| 000000н           | Port 0 data register                                       | PDR0          | R/W*     | Port 0             | XXXXXXX       |

| 000001н           | Port 1 data register                                       | PDR1          | R/W*     | Port 1             | XXXXXXX       |

| 000002н           | Port 2 data register                                       | PDR2          | R/W*     | Port 2             | XXXXXXX       |

| 000003н           | Port 3 data register                                       | PDR3          | R/W*     | Port 3             | XXXX          |

| 000004н           | Port 4 data register                                       | PDR4          | R/W!     | Port 4             | XXXXXXX       |

| 000005н           | Port 5 data register                                       | PDR5          | R/W*     | Port 5             | 11111111      |

| 000006н           | Port 6 data register/<br>Port data buffer register         | PDR6/<br>PDBR | R/W*     | Port 6             | -xxxxxx       |

| 000007н<br>to 0Fн | Vacancy                                                    | _             | *1       | _                  | _             |

| 000010н           | Port 0 direction register                                  | DDR0          | R/W      | Port 0             | 00000000      |

| 000011н           | Port 1 direction register                                  | DDR1          | R/W      | Port 1             | 0000000       |

| 000012н           | Port 2 direction register                                  | DDR2          | R/W      | Port 2             | 00000000      |

| 000013н           | Port 3 direction register                                  | DDR3          | R/W      | Port 3             | 0000          |

| 000014н           | Port 4 direction register                                  | DDR4          | R/W      | Port 4             | 0000          |

| 000015н           | Analog input enable register                               | ADER          | R/W      | Port 5             | 11111111      |

| 000016н           | Port 6 direction register                                  | DDR6          | R/W      | Port 6             | -0000000      |

| 000017н<br>to 1Вн | Vacancy                                                    | _             | *1       | _                  | _             |

| 00001Сн<br>to 1Fн | System reserved area                                       | _             | *1       | _                  | _             |

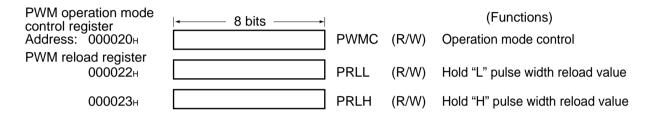

| 000020н           | PWM operation mode control register                        | PWMC          | R/W      |                    | 000001        |

| 000021н           | Vacancy                                                    | _             | *1       | PWM                | _             |

| 000022н           | PWM reload register                                        | PRLL          | R/W      |                    | XXXXXXX       |

| 000023н           | 1 WWW reload register                                      | PRLH          | R/W      |                    | XXXXXXX       |

| 000024н           | Serial mode register                                       | SMR           | R/W!     |                    | 00000-00      |

| 000025н           | Serial control register                                    | SCR           | R/W!     |                    | 00000100      |

| 000026н           | Serial input data register/<br>Serial output data register | SIDR/<br>SODR | R/W      | UART               | xxxxxxx       |

| 000027н           | Serial status register                                     | SSR           | R/W!     |                    | 00001-00      |

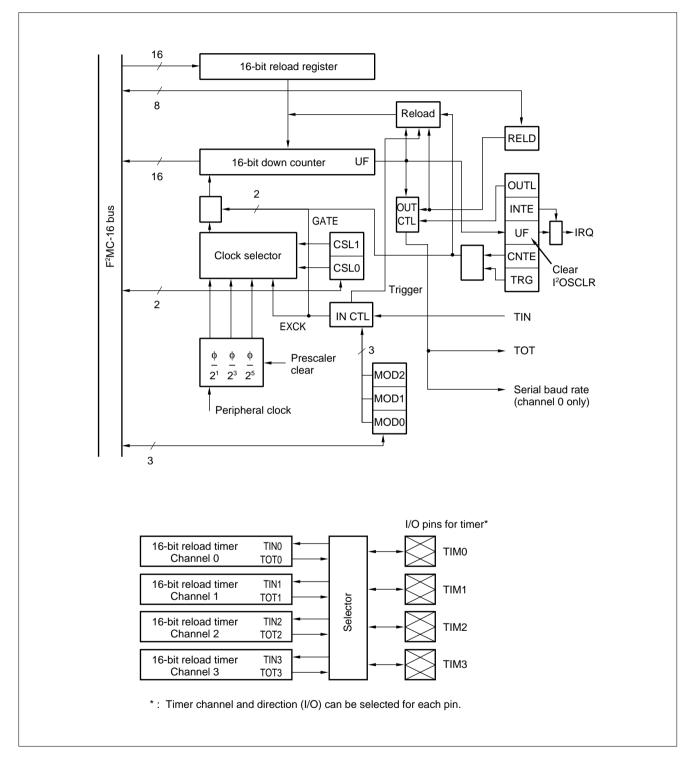

| 000028н           | Interrupt enable register                                  | ENIR          | R/W      | External interrupt | 00000000      |

| 000029н           | Interrupt source register                                  | EIRR          | R/W      |                    | XXXXXXX       |

| 00002Ан           | Poguact lovel patting register                             | ELVR          | R/W      | External interrupt | 00000000      |

| 00002Вн           | Request level setting register                             | ELVK          | FX/VV    |                    | 00000000      |

| 00002Сн           | A/D control atotus register                                | ADCS          | R/W!     | A/D converter      | 00000000      |

| 00002Dн           | A/D control status register                                | 7003          | [N/ VV!  | A/D converter      | 00000000      |

#### (Continued)

| Address | Register Name Acce                     |         | Access*2 | Resource name  | Initial value |

|---------|----------------------------------------|---------|----------|----------------|---------------|

| 00002Ен | A/D data register                      | ADCD    | DAM      | A/D convertor  | XXXXXXX       |

| 00002Fн | A/D data register                      | ADCR    | R/W!     | A/D converter  | 00000XX       |

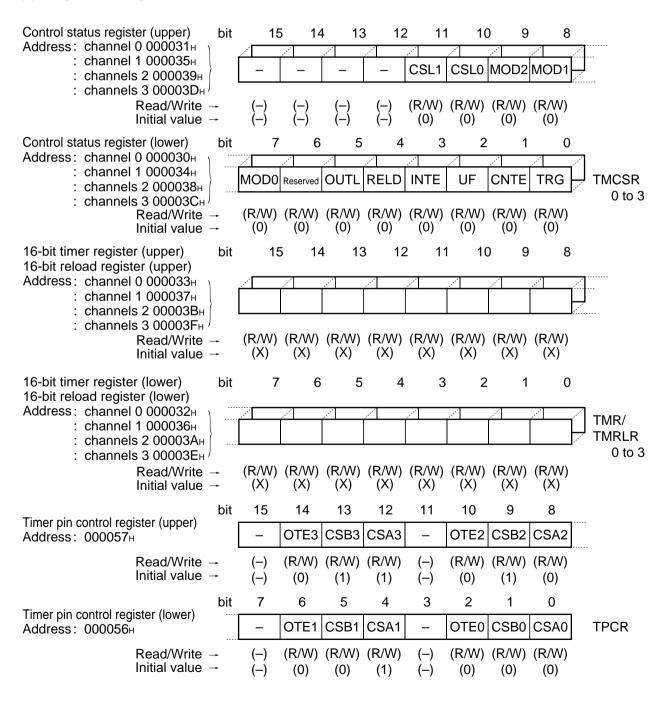

| 000030н | Control atatus register                | TMCCDO  | DAM      |                | 00000000      |

| 000031н | Control status register                | TMCSR0  | R/W      | 16-bit         | 0000          |

| 000032н | 16-bit timer register/                 | TMR0/   | DAM      | reload timer 0 | XXXXXXX       |

| 000033н | 16-bit reload register                 | TMRLR0  | R/W      |                | XXXXXXX       |

| 000034н | Control status assistes TMCCD4 DAM     |         | 00000000 |                |               |

| 000035н | Control status register                | TMCSR1  | R/W      | 16-bit         | 0000          |

| 000036н | 16-bit timer register/                 | TMR1/   | DAM      | reload timer 1 | XXXXXXX       |

| 000037н | 16-bit reload register                 | TMRLR1  | R/W      |                | XXXXXXX       |

| 000038н | Cantal status as sister                | TMOCDO  | DAM      |                | 0000000       |

| 000039н | Control status register                | TMCSR2  | R/W      | 16-bit         | 0000          |

| 00003Ан | 16-bit timer register/                 | TMR2/   | DAM      | reload timer 2 | XXXXXXX       |

| 00003Вн | 16-bit reload register                 | TMRLR2  | R/W      |                | XXXXXXX       |

| 00003Сн | 0                                      | T1400D0 | D 444    |                | 00000000      |

| 00003Dн | Control status register                | TMCSR3  | R/W      | 16-bit         | 0000          |

| 00003Ен | 16-bit timer register/                 | TMR3/   | 5.44     | reload timer 3 | xxxxxxx       |

| 00003Fн | 16-bit reload register                 | TMRLR3  | R/W      |                | XXXXXXX       |

| 000040н | Timer control status register          | TCSR    | R/W!     |                | 10000000      |

| 000041н | Compare interrupt control register     | CICR    | R/W      |                | 00000000      |

| 000042н | Timer mode control register            | TMCR    | R/W!     |                | 001-0000      |

| 000043н | Compare/data select register           | COER    | R/W      |                | 0000          |

| 000044н | Compare buffer mode control register   | CMCR    | R/W      |                | 0000          |

| 000045н | Zero detect output control register    | ZOCTR   | W        |                | X0000         |

| 000046н | Output control buffer register         | OCTBR   | R/W      | Multi-function | 11111111      |

| 000047н | Zero detect interrupt control register | ZICR    | R/W!     | timer          | 0 X X X X     |

| 000048н | Output compare buffer register 0       | OCDDDO  | W        |                | xxxxxxx       |

| 000049н | Output compare buffer register 0       | OCPBR0  | VV       |                | XXXXXX        |

| 00004Ан | Output compare buffer register 4       | OCDDD4  | \^/      |                | xxxxxxx       |

| 00004Вн | Output compare buffer register 1       | OCPBR1  | W        |                | XXXXX         |

| 00004Сн | Output company by the resistant of     | OCDDDC  | \^/      |                | xxxxxxx       |

| 00004Дн | Output compare buffer register 2       | OCPBR2  | W        |                | XXXXXX        |

# To Top / Lineup / Index MB90660A Series

#### (Continued)

| Address           | Register                                          | Name   | Access*2 | Resource name                      | Initial value |  |

|-------------------|---------------------------------------------------|--------|----------|------------------------------------|---------------|--|

| 00004Ен           | Output compare buffer register 2                  | OCDBD2 | W        |                                    | XXXXXXX       |  |

| 00004Fн           | Output compare buffer register 3                  | OCPBR3 | VV       |                                    | XXXXXX        |  |

| 000050н           | Common close buffer register                      | CLDDD  | 10/      |                                    | 00000000      |  |

| 000051н           | Compare clear buffer register                     | CLRBR  | W        | Multi-function timer               | 000000        |  |

| 000052н           | Dead time control register                        | DTCR   | R/W!     |                                    | 00000000      |  |

| 000053н           | Dead time setting register                        | DTSR   | W        |                                    | XXX0XXXX      |  |

| 000054н           | Dead time compare register                        | DTCMR  | W        |                                    | XXXXXXXX      |  |

| 000055н           | Vacancy                                           | _      | *1       | _                                  | _             |  |

| 000056н           | Times nin central register                        | TDCD   | DAM      | 16-bit reload                      | -001-000      |  |

| 000057н           | Timer pin control register                        | TPCR   | R/W      | timer                              | -011-010      |  |

| 000058н<br>to 5Ен | Vacancy                                           | _      | *1       | _                                  | _             |  |

| 00005Fн           | Machine clock division control register           | CDCR   | W        | UART                               | 1111          |  |

| 000060н<br>to 8Fн | Vacancy                                           | _      | *1       | _                                  | _             |  |

| 000090н<br>to 9Ен | System reserved area                              | _      | *1       | _                                  | _             |  |

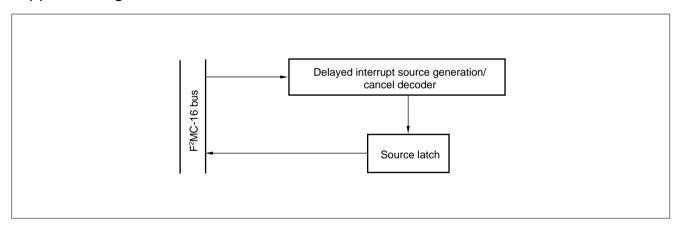

| 00009Fн           | Delayed interrupt source generate/cancel register | DIRR   | R/W      | Delayed interrupt generator module | 0             |  |

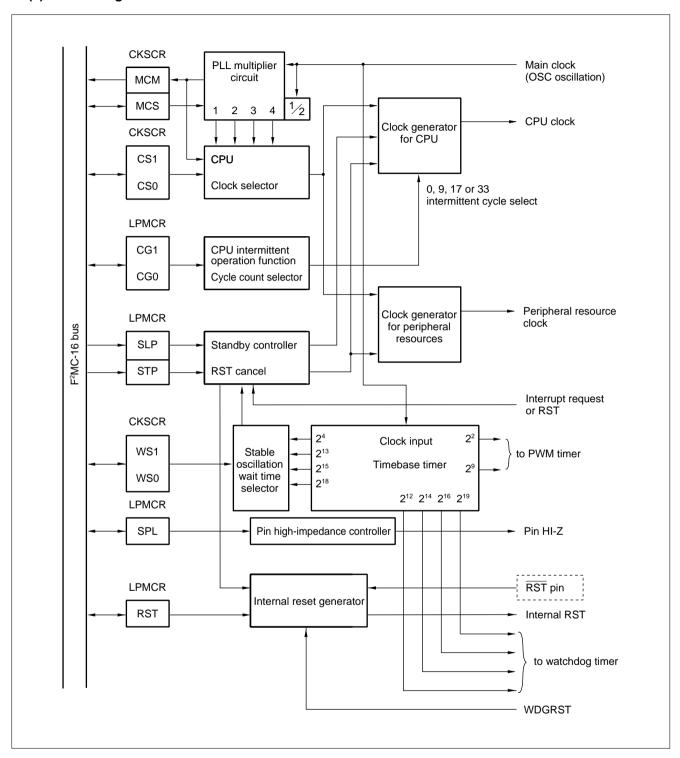

| 0000А0н           | Low power mode control register                   | LPMCR  | R/W!     | I am manuar                        | 00011000      |  |

| 0000А1н           | Clock select register                             | CKSCR  | R/W!     | Low power                          | 11111100      |  |

| 0000A2н<br>to A7н | System reserved area                              | _      | *1       | _                                  | _             |  |

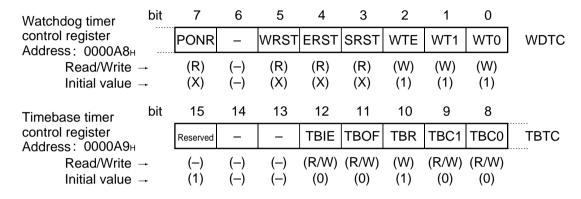

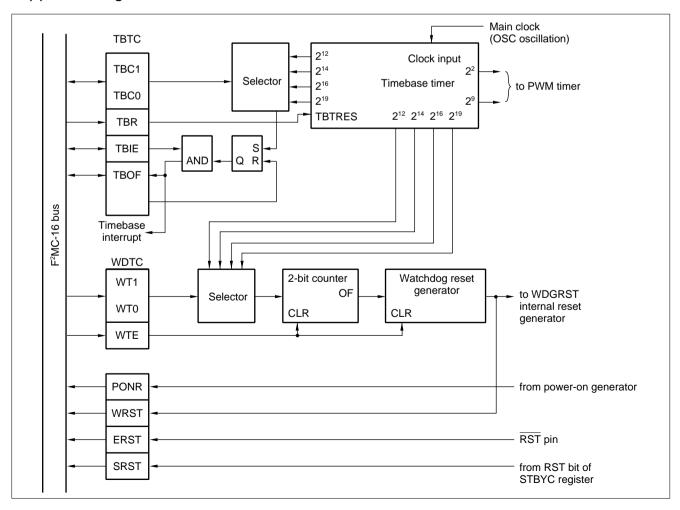

| 0000А8н           | Watchdog timer control register                   | WDTC   | R/W!     | Watchdog timer                     | X-XXX111      |  |

| 0000А9н           | Timebase timer control register                   | TBTC   | R/W!     | Timebased timer                    | 100100        |  |

| 0000AAн<br>to AFн | System reserved area                              | _      | *1       | _                                  | _             |  |

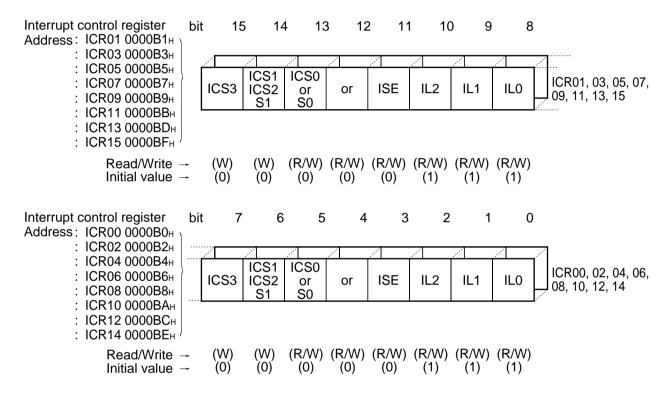

| 0000В0н           | Interrupt control register 00                     | ICR00  | R/W!     |                                    | 00000111      |  |

| 0000В1н           | Interrupt control register 01                     | ICR01  | R/W!     |                                    | 00000111      |  |

| 0000В2н           | Interrupt control register 02                     | ICR02  | R/W!     |                                    | 00000111      |  |

| 0000ВЗн           | Interrupt control register 03                     | ICR03  | R/W!     | Interrupt                          | 00000111      |  |

| 0000В4н           | Interrupt control register 04                     | ICR04  | R/W!     | controller                         | 00000111      |  |

| 0000В5н           | Interrupt control register 05                     | ICR05  | R/W!     |                                    | 00000111      |  |

| 0000В6н           | Interrupt control register 06                     | ICR06  | R/W!     |                                    | 00000111      |  |

| 0000В7н           | Interrupt control register 07                     | ICR07  | R/W!     |                                    | 00000111      |  |

#### (Continued)

| Address           | Register                      | Name  | Access*2 | Resource name | Initial value |

|-------------------|-------------------------------|-------|----------|---------------|---------------|

| 0000В8н           | Interrupt control register 08 | ICR08 | R/W!     |               | 00000111      |

| 0000В9н           | Interrupt control register 09 | ICR09 | R/W!     |               | 00000111      |

| 0000ВАн           | Interrupt control register 10 | ICR10 | R/W!     |               | 00000111      |

| 0000ВВн           | Interrupt control register 11 | ICR11 | R/W!     | Interrupt     | 00000111      |

| 0000ВСн           | Interrupt control register 12 | ICR12 | R/W!     | controller    | 00000111      |

| 0000ВDн           | Interrupt control register 13 | ICR13 | R/W!     |               | 00000111      |

| 0000ВЕн           | Interrupt control register 14 | ICR14 | R/W!     |               | 00000111      |

| 0000ВFн           | Interrupt control register 15 | ICR15 | R/W!     |               | 00000111      |

| 0000C0н<br>to FFн | System reserved area          | _     | *1       | _             | _             |

- \*1: Access prohibited

- \*2: Registers marked "R/W!" in the access column include some bits that can only be read or only be written. For details, see the register list for each resource.

- \*: When a register marked "R/W!", "R/W\*" or "W" in the access column is accessed by a read-modify-write instruction (such as a bit set instruction), the bit operated on by the instruction will be set to the specified value, but a malfunction will occur if there are any other bits which can only be written. Therefore, do not access these locations using these instructions.

#### **Description of Initial Values**

- 0: The initial value of this bit is "0".

- 1: The initial value of this bit is "1".

- \*: The initial value of this bit is "1" or "0". (This is determined depending on the level of the MD0 to MD2 pins.)

- X: The initial value of this bit is undefined.

- -: This bit is not used. The initial value is undefined.

Note: The initial value results for bits which can only be written when initialized by a reset. Note that this is not the value when read.

Also, sometimes LPMCR, CKSCR and WDTC are initialized and sometimes they are not depending on the type of reset. If they are initialized, the initial value is used.

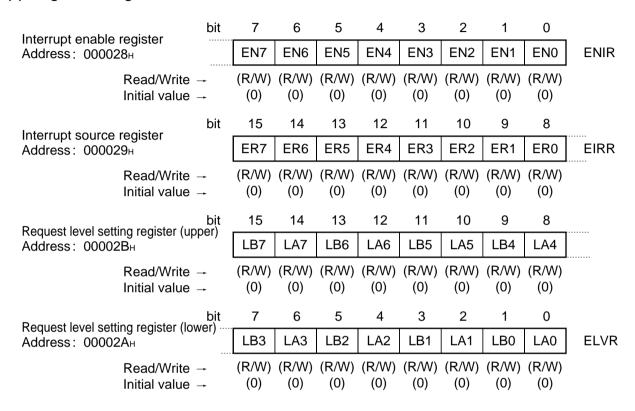

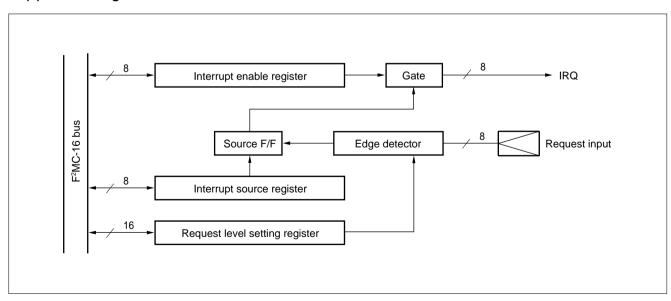

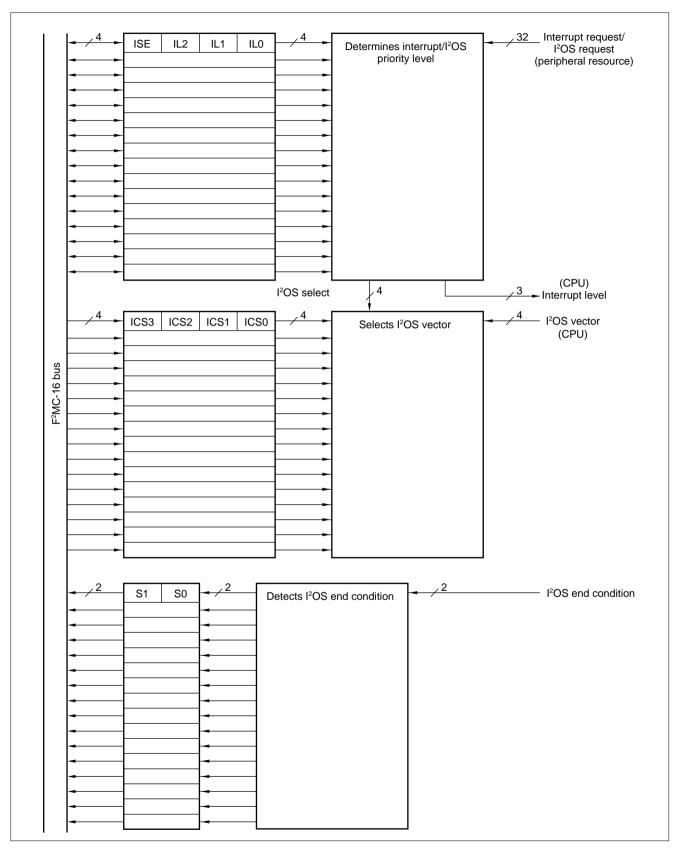

## ■ INTERRUPT SOURCES, INTERRUPT VECTORS AND INTERRUPT CONTROL REGISTERS

| Intermed accord                                             | I <sup>2</sup> OS | I   | nterrupt        | vector              | Interrupt control register |           |  |

|-------------------------------------------------------------|-------------------|-----|-----------------|---------------------|----------------------------|-----------|--|

| Interrupt source                                            | support           | Nur | nber            | Address             | ICR                        | Address   |  |

| Reset                                                       | ×                 | #08 | 08н             | FFFFDCH             | _                          | _         |  |

| INT9 instruction                                            | ×                 | #09 | 09н             | FFFFD8 <sub>H</sub> | _                          | _         |  |

| Exception                                                   | ×                 | #10 | ОАн             | FFFFD4 <sub>H</sub> | _                          | _         |  |

| Multi-function timer DTTI input                             | ×                 | #12 | 0Сн             | FFFFCCH             | ICR00                      | 0000В0н   |  |

| External interrupt #0                                       | 0                 | #13 | 0Дн             | FFFFC8 <sub>H</sub> | ICR01                      | 0000В1н   |  |

| External interrupt #4                                       | 0                 | #14 | 0Ен             | FFFFC4 <sub>H</sub> | - ICRUI                    | 0000BTH   |  |

| Multi-function timer trigger input or zero detect           | 0                 | #15 | 0Гн             | FFFFC0 <sub>H</sub> | ICR02                      | 0000В2н   |  |

| Multi-function timer zero detect                            | 0                 | #17 | 11н             | FFFFB8 <sub>H</sub> | ICR03                      | 0000ВЗн   |  |

| Multi-function timer overflow, compare clear or zero detect | 0                 | #19 | 13н             | FFFFB0 <sub>H</sub> | ICR04                      | 0000В4н   |  |

| External interrupt #1                                       | 0                 | #21 | 15н             | FFFFA8 <sub>H</sub> | ICR05                      | 0000В5н   |  |

| Multi-function timer compare match                          | ×                 | #22 | 16н             | FFFFA4 <sub>H</sub> |                            | 000000011 |  |

| External interrupt #5                                       | 0                 | #23 | 17н             | FFFFA0 <sub>H</sub> | ICR06                      | 0000В6н   |  |

| PWM underflow                                               | ×                 | #24 | 18н             | FFFF9C <sub>H</sub> |                            |           |  |

| External interrupt #2                                       | 0                 | #25 | 19н             | FFFF98 <sub>H</sub> | ICR07                      | 0000В7н   |  |

| External interrupt #6                                       | 0                 | #26 | 1Ан             | FFFF94 <sub>H</sub> | - ICKUI                    | 0000B7H   |  |

| 16-bit reload timer #0                                      | 0                 | #27 | 1Вн             | FFFF90 <sub>H</sub> | ICR08                      | 0000В8н   |  |

| 16-bit reload timer #1                                      | 0                 | #28 | 1Сн             | FFFF8C <sub>H</sub> | ICKUO                      | ООООБОН   |  |

| 16-bit reload timer #2                                      | 0                 | #29 | 1Dн             | FFFF88 <sub>H</sub> | ICR09                      | 0000В9н   |  |

| 16-bit reload timer #3                                      | 0                 | #30 | 1Ен             | FFFF84 <sub>H</sub> |                            | 0000D9H   |  |

| End of A/D converter conversion                             | 0                 | #31 | 1F <sub>H</sub> | FFFF80 <sub>H</sub> | ICR10                      | 0000ВАн   |  |

| Timebase timer interval interrupt                           | ×                 | #34 | 22н             | FFFF74 <sub>H</sub> | ICR11                      | 0000ВВн   |  |

| UART send complete                                          | 0                 | #35 | 23н             | FFFF70 <sub>H</sub> | ICR12                      | 0000ВСн   |  |

| UART receive complete                                       | 0                 | #37 | 25н             | FFFF68 <sub>H</sub> | ICR13                      | 0000ВДн   |  |

| External interrupt #3                                       | 0                 | #39 | 27н             | FFFF60 <sub>H</sub> | ICR14                      | 0000ВЕн   |  |

| External interrupt #7                                       | 0                 | #40 | 28н             | FFFF5C <sub>H</sub> | 10814                      | UUUUDEH   |  |

| Delayed interrupt generator module                          | ×                 | #42 | 2Ан             | FFFF54 <sub>H</sub> | ICR15                      | 0000ВFн   |  |

<sup>:</sup> indicates that the interrupt request flag is cleared by the I2OS interrupt clear signal (no stop request).

Note: Do not specify I<sup>2</sup>OS activation in interrupt control registers that do not support I<sup>2</sup>OS.

②: indicates that the interrupt request flag is cleared by the I2OS interrupt clear signal (with stop request).

$<sup>\</sup>times$ : indicates that the interrupt request flag is not cleared by the I<sup>2</sup>OS interrupt clear signal.

#### **■ PERIPHERAL RESOURCES**

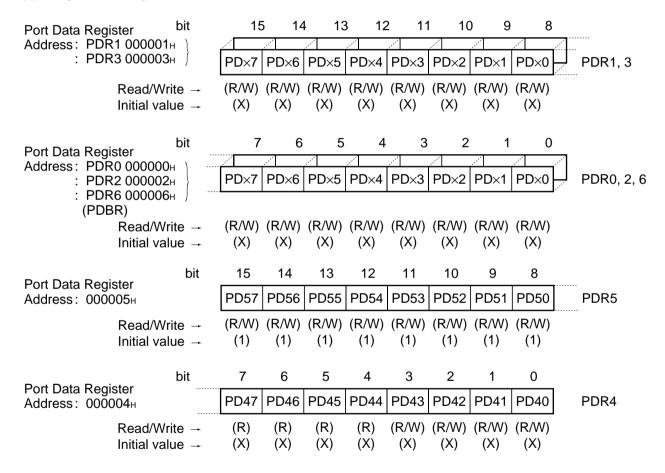

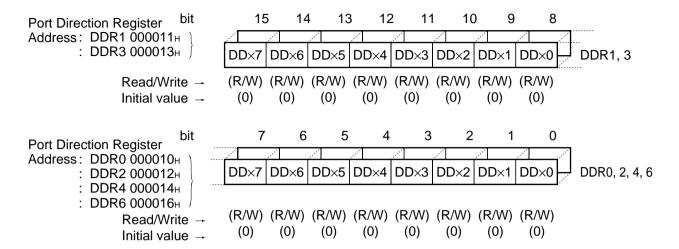

#### 1. Parallel Port

The MB90660A includes 39 I/O pins, 4 input pins, and 8 open-drain output pins.

Port 0, 1, 2, 3 and 6 are I/O ports. They are used for input when the corresponding direction register value is "0", and for output when the value is "1".

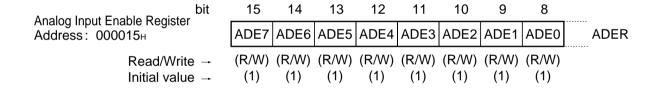

Port 5 is an open-drain port. It is used as a port when the analog input enable register is "0".

Ports 40 to 43 are I/O ports. They are used for input when the corresponding direction register value is "0", and for output when the value is "1". Ports 44 to 47 are input ports which can only be used for reading data.

#### (1) Register Configuration

Notes: There are no register bits for bits 15 to 12 of Port 3.

There is no register bit for bit 7 of Port 6.

Bits 7 to 4 of Port 4 can only be used to read data.

Notes: There are no register bits for bits 15 to 12 of Port 3.

There are not register bits for bits 7 to 4 of Port 4

There is no DDR for Port 5.

There is no register bit for bit 7 of Port 6.

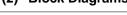

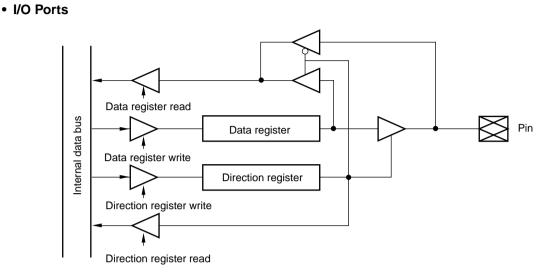

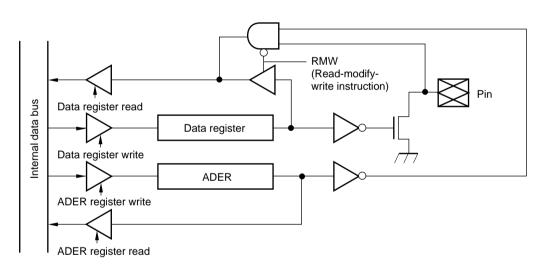

#### (2) Block Diagrams

• Open-drain Ports (Also Used for Analog Input)

• Input Ports

#### 2. Multi-function Timer

The multi-function timer controls up to 7 realtime output pins, and includes the following functions.

Interval timer function

It can output pulses or generate an interrupt at a fixed interval.

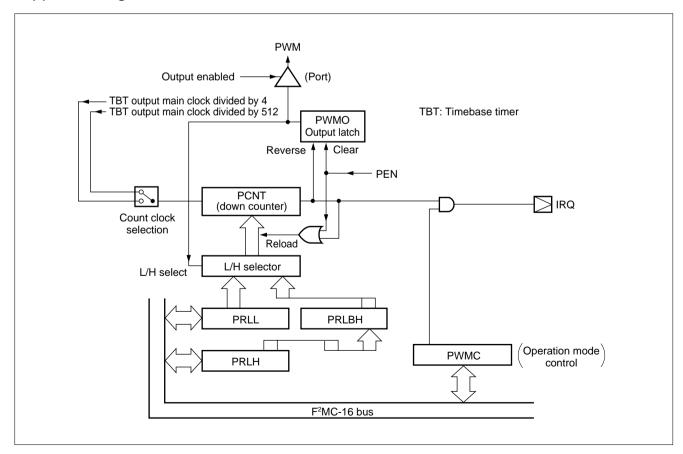

· PWM output function

Can perform output for a fixed cycle pulse while changing the duty ratio (ratio between "L" output width and "H" output width) in realtime.

3-phase AC sine wave output (inverter control output) function

Can perform 3-phase AC sine wave output using AC motor inverter control, etc. (using any setting for the non-overlap interval)

This timer also has the following characteristics.

• Pulse cycle control using 14-bit timer

A machine cycle of 1, 2, 8 or 16 can be selected based on pre-scalars as the clock source (Minimum resolution of 62.5 ns at 16 MHz operation).

Can use a carrier frequency up to 30 KHz at 8-bit stop when used for AC motor control.

Up count only or up/down count can be selected using the count mode selection.

Possessing a buffer, cycle can be changed in realtime by transferring data from buffer upon zero detect.

· Duty control using compare registers

Possessing four compare registers, output pulse duty can be set for four separate channels.

Each possessing a separate buffer, duty can be changed in realtime by transferring data from buffer upon zero detect or comparison.

· Non-overlap control using dead time timer

Dead time timer can be used to generate PWM output for three channels or even reversed signals with non-overlap, thus allowing an AC motor control wave (U, V, W, X, Y, Z) to be generated.

A machine cycle of 1, 4, 8 or 32 can be selected based on pre-scalars as the clock source for the dead timer (Minimum resolution of 62.5 ns at 16 MHz operation)

Forced stop control using DTTI pin input

The forced pin output level can be fixed by DTTI pin input or software.

Inactive control can be performed during AC motor control using DTTI pin input.

External pin control even during vibration stop can be performed through clockless DTTI pin input.

Event detection and interrupt generation using various flags

Flags can be set and/or interrupts generated upon zero detect, overflow, detect of match with compare registers, or clear by TRG pin input, or any match of the compare registers for the four channels for the 14-bit timer (also possible to disable interrupt output).

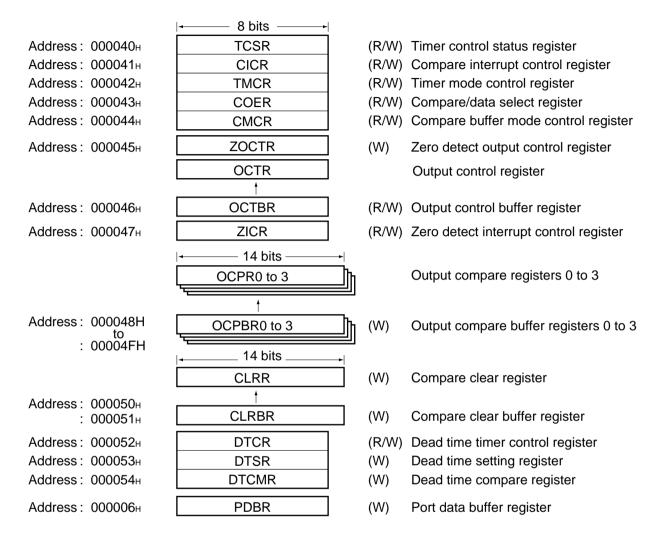

#### (1) Register Configuration

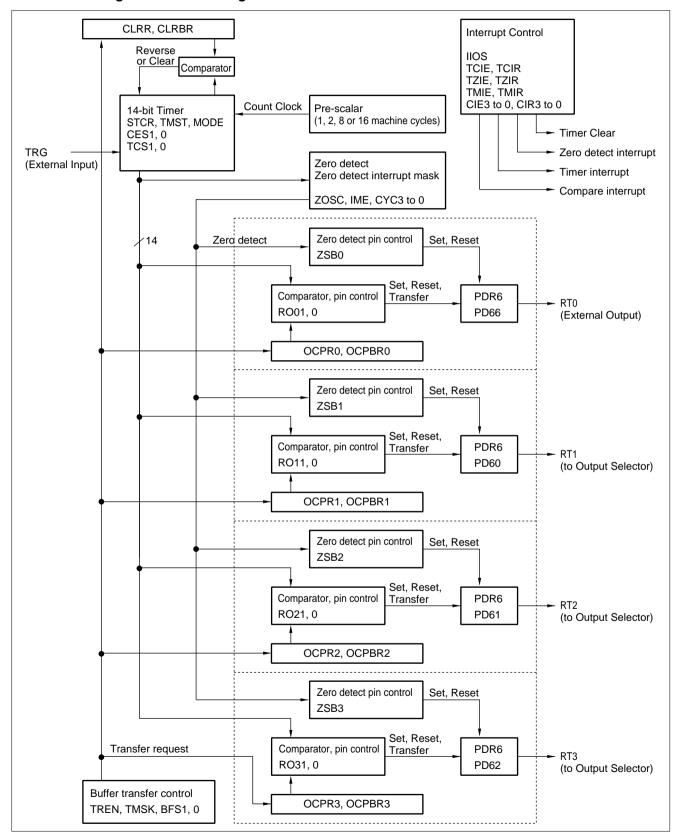

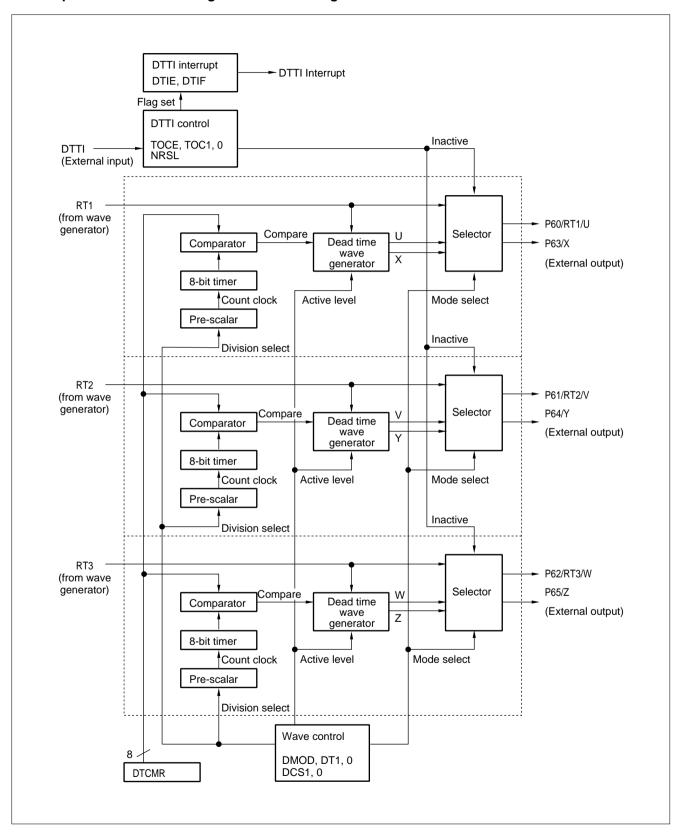

#### (2) Block Diagrams

• Timer/wave generator block diagram

• Output selector/dead time generator block diagram

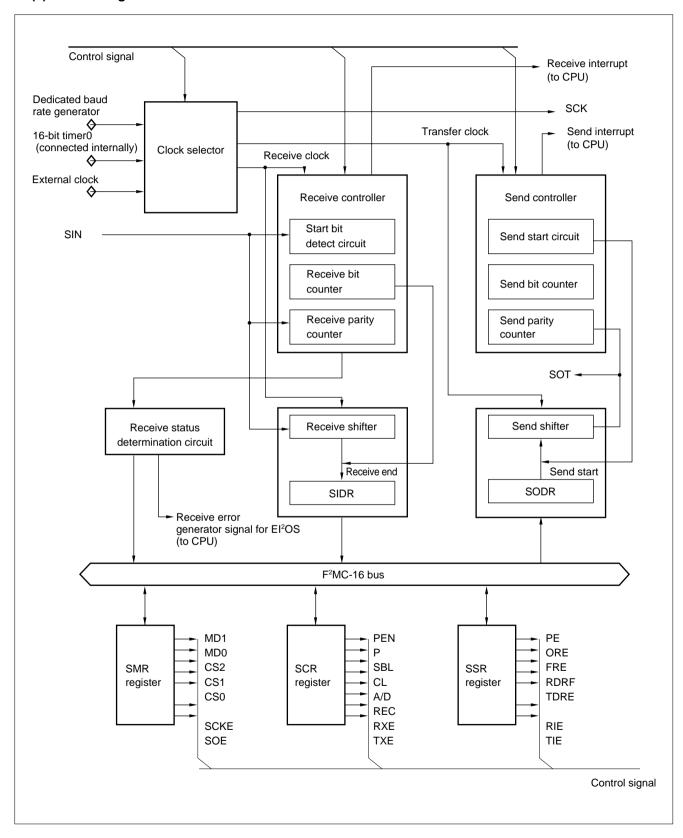

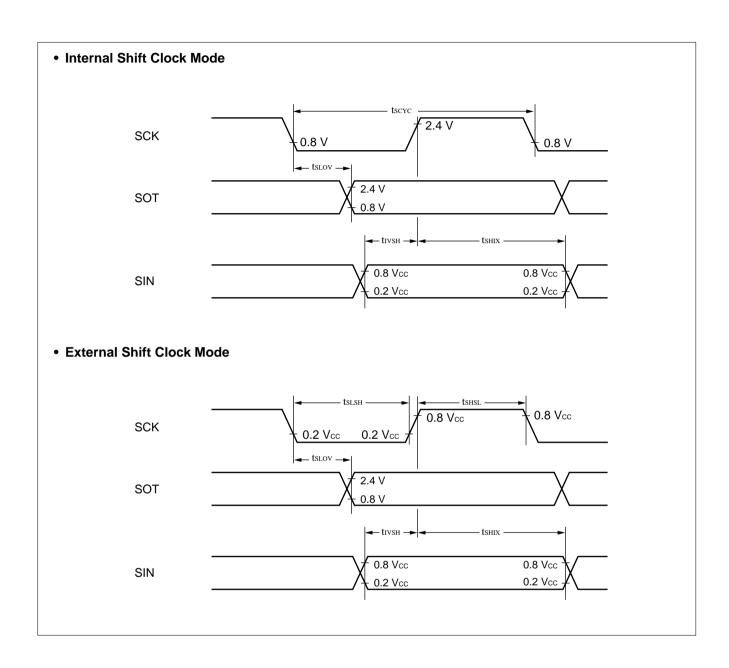

#### 3. UART

The UART is a serial I/O port for asynchronous (start/stop) or CLK synchronous communications with external resources. It has the following characteristics:

- Full duplex double buffering

- Asynchronous (start/stop) or CLK synchronous communications

- Multiprocessor mode support

- Internal dedicated baud-rate generator

Asynchronous : 19230/9615/31250/4808/2404/1202 bps

CLK synchronous : 2 M/1 M/500 K/250 K bps

- · Free baud-rate setting based on external clock

- Error detection functions (parity, framing and overrun)

- Use of NRZ coded transfer signal

- Supports intelligent I/O services

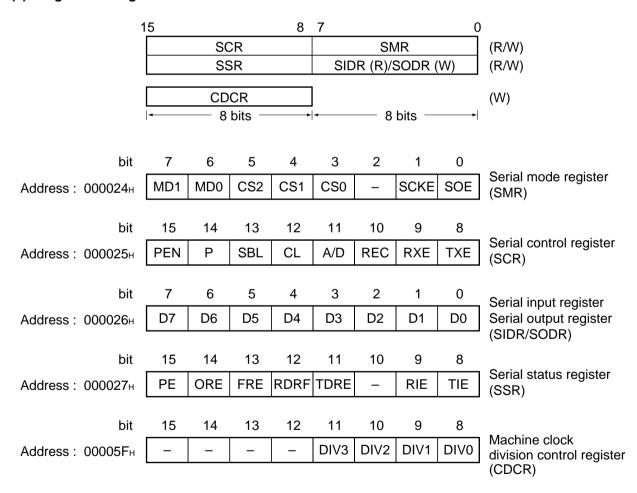

#### (1) Register Configuration

#### (2) Block Diagram

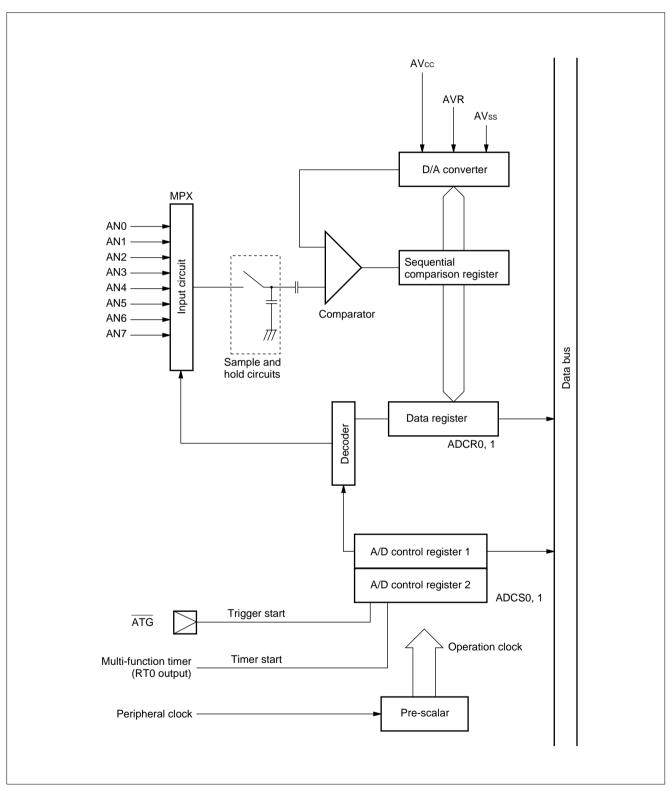

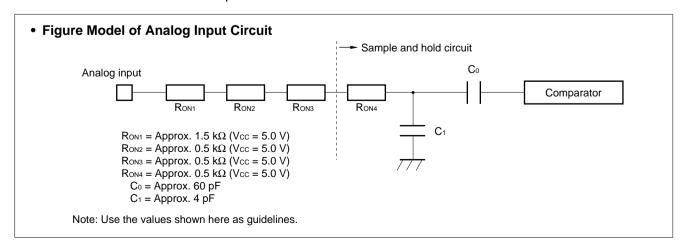

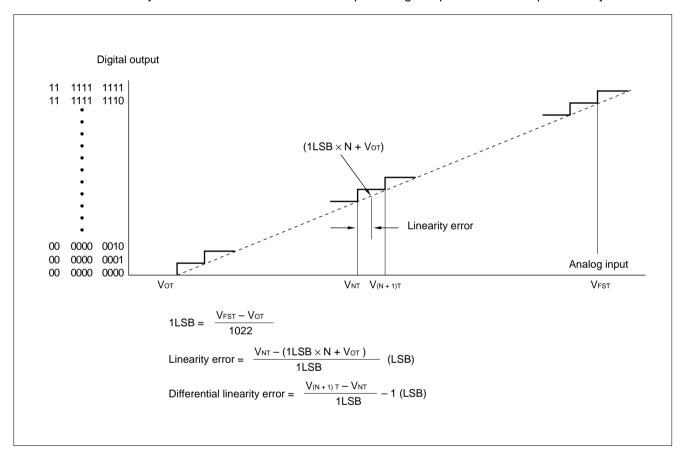

#### 4. 10-bit, 8-channel A/D Converter (with 8-bit Resolution Mode)

This 10-bit, 8-channel A/D converter is used to convert analog input voltage to corresponding digital values. It has the following features.

- $\bullet$  Conversion time: 6.13  $\mu s$  per channel (includes sample and hold time at 98 machine cycles/machine clock of 16 MHz)

- Sample hold time: 3.75 μs per channel (60 machine cycles per machine clock of 16 MHz)

- RC-type sequential approximation conversion with sample and hold circuits

- 10-bit or 8-bit resolution

- Analog input can be selected from 8 channels

Single conversion mode : One channel selected for conversion

Scan conversion mode : Consecutive multiple channels converted (programmable with max. eight

channels)

Repetitive conversion mode: Data on the specified channel is converted repeatedly

Stop conversion mode : Once one channel is converted, operations stop and the device waits until

started again (conversion start can be synchronized)

At the end of each A/D conversion, an interrupt request to the CPU can be generated. This interrupt can be

used to activate I<sup>2</sup>OS or transfer A/D conversion results to memory, making it useful when continuous